数字电子学/同步器件/寄存器

寄存器是由基本数字门组成的数字器件,用于执行任务或功能。

在某些情况下,可能需要规定锁存器何时可以锁存,何时不能锁存。门控SR锁存器是SR锁存器的一个简单扩展,它提供了一个使能线,该线必须驱动为高电平才能锁存数据。即使现在需要控制线,SR锁存器也不是同步的,因为即使在使能脉冲的中间,输入也可以改变输出。

当使能输入为低电平时,来自与门的输出也必须为低电平,因此Q和Q输出保持锁存到先前的数据。只有当使能输入为高电平时,锁存器的状态才能改变,如真值表所示。当使能线被断言时,门控SR锁存器与SR锁存器的工作方式相同。

使能线有时是时钟信号,但通常是读或写选通。

使能 S R Q Q 0 0 0 锁存 0 0 1 锁存 0 1 0 锁存 0 1 1 锁存 1 0 0 锁存 1 0 1 0 1 1 1 0 1 0 1 1 1 亚稳态

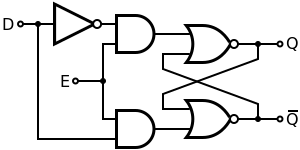

D锁存器(D代表“数据”)或透明锁存器是对门控SR锁存器的简单扩展,它消除了无效输入状态的可能性。

由于门控SR锁存器允许我们在不使用S或R输入的情况下锁存输出,我们可以通过使用互补驱动器驱动置位和复位两个输入来移除其中一个输入:我们移除一个输入,并自动使其成为剩余输入的逆输入。

D锁存器在使能线为高电平时输出D输入,否则输出为使能输入最后一次为高电平时D输入的值。这就是为什么它也被称为透明锁存器 - 当使能被断言时,锁存器被称为“透明” - 信号直接穿过它,就像它不存在一样。

使能 D Q Q 0 0 锁存 0 1 锁存 1 0 0 1 1 1 1 0

D锁存器经常用在集成电路的I/O端口,并且作为离散器件提供,通常是多封装的。例如,74HC75是7400系列IC的一部分,包含四个独立的D锁存器。

T触发器是一种器件,它在每次触发时都会交换或“翻转”状态,如果T输入被断言,否则它将保持当前输出。这种行为由特征方程描述

并且可以用以下任一表格描述

|

|

当T保持为高电平时,触发器将时钟频率除以二;也就是说,如果时钟频率为4 MHz,则从触发器获得的输出频率将为2 MHz。这种“除以”功能在各种类型的数字计数器中都有应用。T触发器也可以使用JK触发器(J & K引脚连接在一起并充当T)或D触发器(T输入和Qprev通过异或门连接到D输入)构建。

JK触发器是对SR触发器的简单改进,其中状态J=K=1并不被禁止。它的工作方式与SR触发器相同,J作为置位输入,K作为复位输入。唯一的区别是,对于以前的“禁止”组合J=K=1,该触发器现在执行一个动作:它反转其状态。由于JK触发器的行为在所有条件下都是完全可预测的,因此它是大多数逻辑电路设计中首选的触发器类型。但仍然存在一个问题,即在实际测试电路时,两个输出都相同。这是因为在每次传播延迟完成时内部都会发生切换。主要的解决方法是使用主从JK触发器,该触发器通过内置的脉冲时钟功能来覆盖自身(内部)的重复切换。

| J | K | Qnext | 评论 | |

|---|---|---|---|---|

| 0 | 0 | Qprev | 保持状态 | |

| 0 | 1 | 0 | 复位 | |

| 1 | 0 | 1 | 置位 | |

| 1 | 1 | Qprev | 切换 |

| Q | Qnext | J | K | 评论 | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | X | 保持状态 | |

| 0 | 1 | 1 | X | 置位 | |

| 1 | 0 | X | 1 | 复位 | |

| 1 | 1 | X | 0 | 保持状态 |