微处理器设计/ALU

微处理器通常具有一个模块,用于对整数执行算术运算。这是因为许多不同的算术和逻辑运算可以使用类似(如果不是相同)的硬件来执行。执行算术和逻辑运算的组件称为算术逻辑单元,或 ALU。 [1]

ALU 是微处理器中最重要的组件之一,通常是处理器中首先设计的部件。设计完 ALU 后,就可以实现微处理器的其余部分,以将操作数和控制代码提供给 ALU。

ALU 单元通常需要能够执行基本逻辑运算(AND、OR)和加法运算。在输入端包含反相器使相同的 ALU 硬件能够执行减法运算(添加反相操作数)以及 NAND 和 NOR 运算。

基本 ALU 设计包括一个“ALU 切片”集合,每个切片都可以对单个位执行指定的操作。每个操作数的每个位都有一个 ALU 切片。

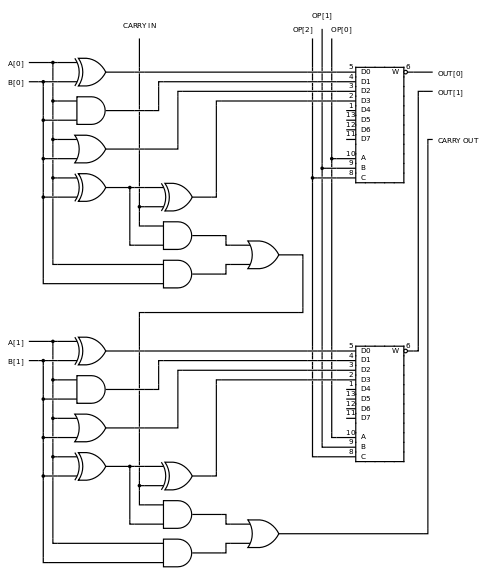

这是一个基本的 2 位 ALU 示例。图像右侧的框是多路复用器,用于选择各种操作:OR、AND、XOR 和加法。

请注意,所有操作都是并行执行的,选择信号 (“OP”) 用于确定将哪个结果传递到数据路径的其余部分。请注意,进位信号(仅用于加法)是为每个操作生成的,并从 ALU 传递出去,因此如果我们不执行加法,就必须忽略进位标志。

这是一个 4 位 ALU 的电路图。

逻辑运算和加法是最简单,也是最常见的运算。因此,典型的 ALU 被设计为专门处理这些运算,而其他运算,如乘法和除法,则在单独的模块中处理。

还要注意,我们在此讨论的 ALU 单元仅适用于整数数据类型,而不是浮点数据。幸运的是,一旦设计了整数 ALU 和乘法器单元,就可以使用这些单元来创建浮点单元 (FPU)。

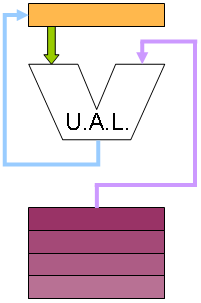

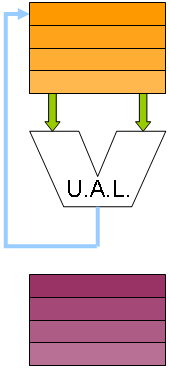

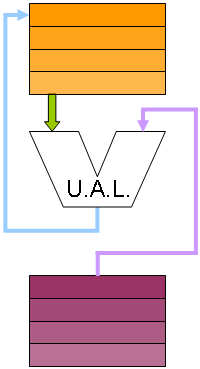

设计完 ALU 后,我们需要定义它如何与处理器的其余部分交互。我们可以选择多种不同的配置,每种配置都有优缺点。每个指令集架构 (ISA) 类别——堆栈、累加器、寄存器-内存或寄存器-寄存器-加载-存储——都需要不同的 ALU 连接方式。 [2] 在下面的所有图像中,橙色表示 CPU 内部内存结构(寄存器),紫色表示外部内存(RAM)。

累加器机器有一个特殊的寄存器,称为累加器。累加器存储每个 ALU 操作的结果,并且也是每个指令的操作数之一。这意味着我们的 ISA 可以更简单,因为指令只需要指定一个操作数,而不是两个操作数和一个目标。累加器架构具有简单的 ISA,并且通常非常快,但是需要编写额外的软件才能将正确的值加载到累加器中。不幸的是,累加器机器很难进行流水线处理。

常见台式计算器可能是使用累加器的一种计算机系统类型。

更常见的架构之一是寄存器到寄存器架构,也称为 3 个寄存器操作数机器。在此配置中,程序员可以指定两个源操作数和一个目标寄存器。不幸的是,ISA 需要扩展以包含两个源操作数和目标操作数的字段。这需要更长的指令字长,并且与累加器相比,还需要额外的努力才能在执行后将结果写回寄存器文件。此写回步骤会导致流水线处理器中的同步问题(我们将在后面讨论流水线)。

寄存器堆栈类似于寄存器到寄存器和累加器结构的组合。在寄存器堆栈中,ALU 从堆栈顶部读取操作数,并将结果压入堆栈顶部。复杂的数学运算需要分解为逆波兰式,这对于程序员来说可能很难使用。但是,许多计算机语言编译器可以轻松地生成逆波兰式,因为内部使用二叉树来表示指令。此外,还需要创建硬件来实现寄存器堆栈,包括 PUSH 和 POP 操作,以及硬件来检测和处理堆栈错误(压入已满的堆栈或弹出空堆栈)。

好处来自高度简化的 ISA。这些机器被称为“0 操作数”或“零地址机器”,因为不需要指定操作数,因为所有操作都作用于指定的堆栈位置。

在右侧的图中,“SP” 是指向堆栈顶部的指针。这只是实现堆栈结构的一种方式,尽管它可能是最简单的方式之一。

一种复杂的结构是寄存器和内存结构,如左侧所示。在此结构中,一个操作数来自寄存器文件,另一个操作数来自外部内存。在此结构中,ISA 很复杂,因为每个指令字都需要能够存储一个完整的内存地址,这可能非常长。在实践中,这种方案不会直接使用,而是通常会集成到其他方案中,例如寄存器到寄存器方案,以提高灵活性。

一些 CISC 架构可以选择将指令的一个操作数指定为内存地址,尽管它们通常被指定为寄存器地址。

还有许多其他结构可用,其中一些是新颖的,另一些是上面列出的类型的组合。设计人员需要决定如何构建微处理器,以及如何将数据馈送到 ALU。

英特尔 IA-32 指令集架构 (x86 处理器) 在浮点运算单元中使用寄存器堆栈架构,但在整数运算中使用修改后的寄存器到寄存器结构。所有整数运算都可以指定一个寄存器作为第一个操作数,以及一个寄存器或内存位置作为第二个操作数。第一个操作数充当累加器,结果存储在第一个操作数寄存器中。这种架构的缺点是指令字长度不统一,这意味着处理器中的指令提取和解码模块需要非常复杂。

典型的 IA-32 指令写成以下形式:

ADD AX, BX

ADD AX, BX

例子: MIPS

[edit | edit source]MIPS 使用寄存器到寄存器结构。每个运算都可以指定两个寄存器操作数,以及一个第三个目标寄存器。缺点是内存读取需要在单独的运算中进行,指令字的小格式意味着空间很宝贵,某些任务难以执行。

MIPS 指令的示例如下:

ADD R1, R2, R3

ADD R1, R2, R3

参考资料

[edit | edit source]- ↑ CPU 设计师使用各种名称来称呼算术逻辑单元,包括“ALU”、“整数执行单元”和“E-box”。Paul V. Bolotoff. "缓存存储器功能原理" 2007.

- ↑ "指令集原理:基本 ISA 类别" by Dr. Sofiène Tahar