微处理器设计/流水线处理器

让我们将我们的微处理器分解成 5 个不同的活动,这些活动通常对应于 5 个不同的硬件部分

- 指令获取 (IF)

- 指令解码 (ID)

- 执行 (EX)

- 内存读写 (MEM)

- 结果回写 (WB)

任何给定的指令在任何时候都只需要其中一个模块,通常按照这个顺序。下面的多周期处理器时序图将更详细地展示这一点

这一切都很好,但在任何时刻,5 个单元中有 4 个处于非活动状态,可能可以用于其他事情。

流水线处理以下任务

- 使用多周期方法来减少单个周期中的计算量。

- 每个周期的计算量更少,允许更快的时钟周期。

- 指令重叠允许处理器的所有组件都在不同的指令上运行。

- 通过更频繁地完成指令来提高吞吐量。

我们将在本章的剩余部分讨论如何实现这些目标。

鉴于我们的多周期处理器,如果我们想让我们的执行重叠,以便同时处理多达 5 条指令,该怎么办?让我们稍微缩短一下我们的时序图来展示这个想法

如该图所示,处理器中的每个元素在每个周期都处于活动状态,处理器的指令速率提高了 5 倍!现在的问题是,为了执行这项任务,我们需要什么额外的硬件?我们需要在每个流水线状态之间添加存储寄存器以存储周期之间的部分结果,我们还需要重新引入单周期 CPU 中的冗余硬件。我们可以继续使用单个内存模块(用于指令和数据),只要我们将内存读取操作限制在周期的前半部分,并将内存写入操作限制在周期的后半部分(反之亦然)。我们可以通过在上一阶段计算内存地址来节省内存访问时间。

寄存器需要保存该点流水线的数据,以及操作剩余流水线所需的控制代码。

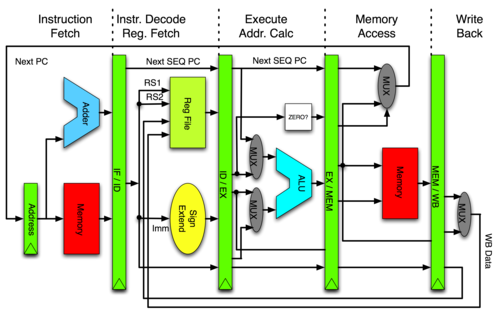

我们得到的处理器设计将类似于以下内容

如果我们有 5 条指令,我们可以使用不同的颜色在我们的流水线中显示它们。在下图中,白色对应于 NOP,不同的颜色对应于流水线中的其他指令。每个阶段,指令都会在流水线中向前移动。

流水线处理器在运行相同软件时,会生成与一次执行一条指令的处理器相同的结果——只是它们生成这些结果的速度快得多。构建流水线处理器的工程师有时会添加特殊的硬件——操作数转发;流水线互锁;等等——为了获得“就像”每条指令都被获取、评估,并且它的结果在获取下一条指令之前就被提交(非重叠)的相同结果——尽管流水线处理器实际上是重叠指令的。

处理器的吞吐量是指一段时间内完成的指令数量。许多处理器被设计成具有每时钟周期一条指令的典型吞吐量,即使任何特定指令都需要多个周期——每个流水线阶段一个周期——从获取到完成的时间。

超级流水线是一种提高流水线深度以提高时钟速度并减少各个阶段延迟的技术。如果 ALU 的执行时间是其他任何模块的三倍,我们可以将 ALU 分成三个独立的阶段,这将减少在较短阶段上浪费的时间。这里的问题是,我们需要找到一种方法将我们的阶段细分为更短的阶段,我们还需要构建更复杂的控制单元来操作流水线并防止所有可能的危险。

现代高端处理器拥有超过 20 个流水线阶段并不少见。

- Jim Plusquellic. "CMSC 611: Advanced Computer Architecture". "流水线简介".

- Jon "Hannibal" Stokes. "流水线:概述(第一部分)".

- Jon Stokes. "流水线:概述(第二部分)".