实用电子学/加法器

加法器是一种将两个位相加并输出结果的设备。被加在一起的位称为“加数”。加法器可以串联在一起,以便将任意长度的两个二进制数相加。

加法器有两种 - 半加器和全加器。半加器只是将两个位相加并给出两个位的输出。全加器将两个输入和来自另一个加法器的进位输入相加,并也给出两个位的输出。

将两个独立的位加在一起时,有四种可能的组合。每种组合都在左侧显示,以及它的解。

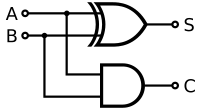

很容易看出,当加数不同时,右边的位(“个位”位)才是 1。因此,将加数异或在一起可以得到右边的位。此位称为 **和**,是加数的 模 2 和(即,如果在超过 1 后循环回到 0,则为解)。

左边的位仅在两个加数均为 1 时才为 1,因此可以使用与门来生成此位,称为 **进位** 位。总结一下

左边的图显示了完整的半加器,其中加数用 A 和 B 表示,和用 S 表示,进位用 C 表示。

真值表如下(括号中的数字是位的权重 - 每个加数为 1,和也为 1 - 进位为 2)

| A (1) | B (1) | S (1) | C (2) | |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 1 |

半加器的缺点是,虽然它们可以生成进位输出,但它们无法处理进位输入信号。这意味着它们只能是独立的单元,并且串联起来以添加多个位数字。

全加器通过将三个数字相加来解决这个问题 - 两个加数与半加器中的加数相同,以及一个进位输入。

全加器可以通过将 A 和 B 连接到一个半加器的输入,将该半加器的和连接到第二个加法器的输入,将进位输入 Cin 连接到另一个输入,并将两个半加器进位输出或运算以给出最终进位输出 Cout 来构建。

下面的图显示了门级全加器。

此处提供了显示两个半加器模块轮廓的此图的版本。此处。全加器的输出是三个一位数字的两位算术和。

此全加器的逻辑表达式为

通过应用布尔代数,第二个语句简化为

在三个数字的输入中,第一个是 A 的状态,第二个是 B 的状态,第三个是 Cin 的状态,下面描述了此全加器的功能

- 所有导致一个 (100, 010, 001) 的组合在和输出处产生高电平,因为只有在第二个异或门处存在一个高电平(当 A 和 B 为低电平时,第一个门给出低电平,当 A 或 B 为高电平时,第一个门给出高电平)在和输出处产生高电平。由于只有一个输入始终为高电平,因此任何与门都不能变为高电平,并且进位输出 Cout 为高电平。

- 所有导致两个 (011, 101, 110) 的组合产生高进位输出和低和

- 011 使第一个异或门变为高电平,因为 A 和 B 不同。结合 Cin 处的“高”电平,这使顶部的与门变为高电平,因此进位输出也变为高电平。第二个异或门处存在两个高电平会使和保持低电平。

- 101 的工作方式与 011 方式完全相同,因为 A 和 B 是可互换的。

- 110:A 和 B 为“高”电平迫使第一个异或门为“低”电平;此“低”电平结合 Cin 的“低”电平在和处产生“低”电平。A 和 B 的“高”电平使底部的与门变为高电平,因此 Cout 为“高”电平。

- 当输入为 111 时,第一个异或门由于两个高输入而变为“低”电平,而第二个异或门变为“高”电平,因为它有一个“低”输入(来自第一个异或门)和一个“高”输入(来自 Cin 输入)。这在和输出处产生“高”电平。A 和 B 均为“高”电平会触发底部的与门,并且进位输出 Cout 也变为“高”电平。

全加器的真值表如下,显示了输入和输出的权重

| A (1) | B (1) | Cin (1) | S (1) | Cout (2) | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 |

如果 A 和 B 均为“高”电平,则连接到它们的与门将输出“高”电平,但异或门将输出“低”电平,迫使另一个与门为“低”电平。如果第一个半加器的“和”输出为“高”电平,则 A 或 B 中必须有一个为“低”电平,这意味着连接到它们的与门被强制为“低”电平。这意味着组合两个半加器进位输出的或门中的两个输入永远不会同时为“高”电平,此门可以用异或门替换(当两个输入均为“高”电平时,或门和异或门不同)。这意味着只需要两种类型的门,并且全加器可以用两个 IC 实现。

这些可以在级联中运行,其中一个级的进位输出驱动下一个级的进位输入。这将在下一节中讨论。

在上一节中,我们介绍了如何将两个一位二进制数相加,同时考虑到来自前一个二进制数量级 (BOOM) 的任何进位以及进位到下一个 BOOM 的任何进位。通过将这些一位加法器串联起来,我们可以制作一个加法器来添加任意长度的二进制数。

为此,将第一级进位输入连接到地,因为在最低有效位之前没有进位。然后将第一级进位输出连接到下一级的进位输入,依此类推,您可以使用任意多的级。

以下是 4 位加法器的布局

请注意,只有在进位输出依次在每个级中注册后,结果才会完整。这种级联效应是这种加法器被称为 **行波进位加法器** 的原因。这需要一点时间,对于大型(32 位或更多)加法器,它可能需要几百纳秒,如果需要高速,这可能是个问题。

有一些速度更快的加法器可以制造,它们没有级联效应,例如 进位超前加法器。

IC 实现

[edit | edit source]The 4008 IC 是一个 4 位全加器,它可以依次与其他加法器串联起来,以提供任意长度的数字。