实用电子学/触发器

触发器是一种存在于两种状态之一的电路,因此可以存储信息。简单的触发器可以用一对与非逻辑门来定义。触发器是非线性电路,这意味着其中一个门的输出被反馈回以与输入信号一起处理。因为触发器在与这个先前输出信号混合的输入信号上运行,所以它们自己的输出依赖于它们之前状态。

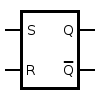

触发器(F/F)是由数字门组成的一种设备,它使用反馈来存储其输入的狀態(1或0)。触发器经常被用来锁存输入数据。这意味着触发器“记住”它的二进制数据,直到被告知“忘记”它。所有触发器至少有一个标记为Q的输出。经常他们有一个标记为/Q的补码。4种基本的触发器是RS、D、反转和JK触发器

配置 数学表达式 真值表

Q = R + Q_

Q_ = S + QSR QQ 00 XX 01 01 10 10 11 00

Q = R . Q_

Q_ = S . QSR QQ 00 00 01 01 10 10 11 XX

最基本的锁存器是简单的SR触发器,其中S和R分别代表置位和复位。它可以用一对交叉耦合的非门来构建。存储的位出现在标记为Q的输出端。

通常,在存储模式下,S和R输入都为低电平,反馈保持Q和Q输出处于恒定状态,其中Q是Q的补码。如果S(置位)在R保持为低电平的情况下被脉冲至高电平,那么Q输出将被强制为高电平,并且即使S返回低电平后也会保持高电平;类似地,如果R(复位)在S保持为低电平的情况下被脉冲至高电平,那么Q输出将被强制为低电平,并且即使R返回低电平后也会保持低电平。

| SR触发器操作[1] | |||||||

|---|---|---|---|---|---|---|---|

| 特性表 | 激励表 | ||||||

| S | R | 动作 | Q(t) | Q(t+1) | S | R | 动作 |

| 0 | 0 | 保持状态 | 0 | 0 | 0 | X | 无变化 |

| 0 | 1 | Q = 0 | 0 | 1 | 1 | 0 | 置位 |

| 1 | 0 | Q = 1 | 1 | 0 | 0 | 1 | 复位 |

| 1 | 1 | 不稳定组合, |

1 | 1 | X | 0 | 无变化 |

('X'表示“不关心”条件;这意味着信号无关紧要)

Q输出始终在时钟上升沿到来时取D输入的狀態。(或者如果时钟输入为低电平有效,则取下降沿)[2] 因此它被称为D触发器,因为输出取D输入或数据输入的值,并将其延迟一个时钟计数。D触发器可以解释为原始的存储单元、零阶保持器或延迟线。

真值表

时钟 D Q Qprev 上升沿 0 0 X 上升沿 1 1 X 非上升沿 X Qprev

('X'表示不关心条件,这意味着信号无关紧要)

这些触发器非常有用,因为它们构成了移位寄存器的基础,而移位寄存器是许多电子设备的重要组成部分。与D型锁存器相比,D触发器的优势在于它在时钟变为高电平时“捕获”信号,并且数据线的后续变化不会影响Q,直到下一个上升沿到来。例外情况是,一些触发器有一个“复位”信号输入,它会复位Q(为零),并且可以是异步的,也可以是与时钟同步的。

上面的电路将寄存器的内容向右移动,每次时钟的有效跃迁移动一位。输入X被移入最左边的位位置。

如果T输入为高电平,则每当时钟输入被选通时,T触发器就会改变状态(“反转”)。如果T输入为低电平,则触发器保持先前值。这种行为可以用特征方程来描述

- (或者,在没有异或运算符的情况下,等效的:)

并可以用真值表来描述

| T触发器操作[1] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 特性表 | 激励表 | |||||||

| 注释 | 注释 | |||||||

| 0 | 0 | 0 | 保持状态(无clk) | 0 | 0 | 0 | 无变化 | |

| 0 | 1 | 1 | 保持状态(无clk) | 1 | 1 | 0 | 无变化 | |

| 1 | 0 | 1 | 反转 | 0 | 1 | 1 | 补码 | |

| 1 | 1 | 0 | 反转 | 1 | 0 | 1 | 补码 | |

当T保持为高电平时,反转触发器将时钟频率除以二;也就是说,如果时钟频率为4 MHz,从触发器获得的输出频率将为2 MHz。这种“除以”特性在各种类型的数字计数器中都有应用。T触发器也可以用JK触发器(J & K引脚连接在一起并充当T)或D触发器(T输入和Qprevious通过异或门连接到D输入)来构建。

JK触发器有2个标记为J和K的输入,以及一个CLK输入(用三角形标记),它由一系列1和0馈送。 和 是互补的,还有SET(S)和RESET(R)输入。 [3]

JK 触发器是对 SR 触发器(J=置位,K=复位)行为的扩展,它将 S = R = 1 的条件解释为“翻转”或切换命令。具体来说,组合 J = 1,K = 0 是将触发器置位的命令;组合 J = 0,K = 1 是将触发器复位的命令;组合 J = K = 1 是将触发器切换的命令,即将其输出更改为其当前值的逻辑补码。将 J = K = 0 设置为不会产生 D 触发器,而是保持当前状态。要合成 D 触发器,只需将 K 设置为 J 的补码。因此,JK 触发器是一种通用触发器,因为它可以配置为 SR 触发器、D 触发器或 T 触发器。注意:触发器是正边沿触发(时钟脉冲),如时序图所示。

JK 触发器的特征方程为

相应的真值表为

| JK 触发器操作 [1] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 特性表 | 激励表 | |||||||

| J | K | Qnext | 注释 | Q | Qnext | J | K | 注释 |

| 0 | 0 | 保持状态 | 0 | 0 | 0 | X | 无变化 | |

| 0 | 1 | 复位 | 0 | 1 | 1 | X | 置位 | |

| 1 | 0 | 置位 | 1 | 0 | X | 1 | 复位 | |

| 1 | 1 | 反转 | 1 | 1 | X | 0 | 无变化 | |

注意:JK 触发器名称的由来由 JPL 工程师 P. L. Lindley 在给电子设计杂志《EDN》的一封信中详细说明。这封信的日期是 1968 年 6 月 13 日,并于当年 8 月的通讯中发表。在这封信中,Lindley 先生解释说他从 Eldred Nelson 博士那里听到了 JK 触发器的故事,Nelson 博士在休斯飞机公司工作期间负责创造了这个术语。当时休斯公司使用的触发器都是后来被称为 J-K 的类型。在设计逻辑系统时,Nelson 博士对触发器的输入分配了字母,如下所示:#1:A & B,#2:C & D,#3:E & F,#4:G & H,#5:J & K。

另一种理论认为,置位和复位输入被赋予了“J”和“K”的符号,因为帮助设计 J-K 触发器的工程师之一名叫 Jack Kilby。

- ↑ a b c Mano, M. Morris (2004). Logic and Computer Design Fundamentals, 3rd Edition. Upper Saddle River, NJ, USA: Pearson Education International. pp. pg283. ISBN 0-13-1911651.

{{cite book}}:|pages=has extra text (help); Unknown parameter|coauthors=ignored (|author=suggested) (help) - ↑ D 触发器

- ↑ D.A.Godse, A.P.Godse 逻辑设计 ISBN 9788184312768