可编程逻辑/FPGA

FPGA 代表 “现场可编程门阵列”,是一种在“现场”可编程(和可重新编程)的 VLSI 类型。FPGA 可以通过使用 HDL 进行编程,这些程序从主机计算机系统下载到 FPGA。

现场可编程门阵列 (FPGA) 是一种半导体器件,包含可编程逻辑组件和可编程互连。可编程逻辑组件可以被编程为复制基本逻辑门的逻辑功能,例如 AND、OR、XOR、NOT 或更复杂的组合功能,例如解码器或简单的数学函数。在大多数 FPGA 中,这些可编程逻辑组件(或 FPGA 行话中的逻辑块)还包括存储器元件,这些元件可能是简单的触发器或更完整的存储器块。

可编程互连的层次结构允许 FPGA 的逻辑块根据系统设计人员的需要进行互连,有点像一个单芯片可编程面包板。这些逻辑块和互连可以在制造过程之后由客户/设计人员进行编程(因此被称为“现场可编程”,即在现场可编程),以便 FPGA 可以执行所需的任何逻辑功能。

FPGA 通常比其专用集成电路 (ASIC) 对手速度慢,不能处理如此复杂的设计,并且功耗更大。但是,它们有几个优点,例如更短的上市时间、能够在现场重新编程以修复错误以及更低的非经常性工程成本。供应商可以销售他们 FPGA 的更便宜、更不灵活的版本,这些版本在设计提交后无法修改。这些设计的开发是在普通 FPGA 上进行的,然后迁移到更类似 ASIC 的固定版本。复杂的可编程逻辑器件 (CPLD) 是另一种选择。

FPGA 的应用包括 DSP、软件定义无线电、航空航天和国防系统、ASIC 原型设计、医学成像、计算机视觉、语音识别、密码学、生物信息学、计算机硬件仿真以及越来越多的其他领域。FPGA 最初作为 CPLD 的竞争对手而出现,并在类似的空间中竞争,即用于 PCB 的粘合逻辑。随着其尺寸、功能和速度的提升,它们开始接管越来越多的功能,以至于现在一些被当作片上系统 (SOC) 来销售。

FPGA 特别适用于可以利用其架构提供的巨大并行性的任何领域或算法。其中一个领域是破解密码,特别是对密码算法进行暴力攻击。

FPGA 也广泛用于系统验证,包括硅前验证、硅后验证和固件开发。这使得芯片公司可以在工厂生产芯片之前验证其设计,从而缩短了上市时间。

应用电路必须映射到具有足够资源的 FPGA。

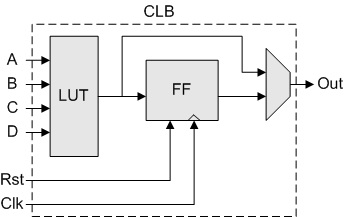

典型的 FPGA 逻辑块由一个 4 输入查找表 (LUT) 和一个触发器组成。

只有一个输出,它可以是寄存器化的或非寄存器化的 LUT 输出。逻辑块有四个 LUT 输入和一个时钟输入。由于时钟信号(以及通常其他高扇出信号)通常通过商用 FPGA 中的专用专用路由网络进行路由,因此它们和其他信号分别进行管理。

每个输入都可以从逻辑块的一侧访问,而输出引脚可以连接到逻辑块右侧和下方的通道中的路由线。

每个逻辑块输出引脚可以连接到与其相邻的通道中的任何一条布线段。

同样,I/O 焊盘可以连接到与其相邻的通道中的任何一条布线段。例如,芯片顶部的 I/O 焊盘可以连接到其正下方水平通道中的任何 W 根线(其中 W 是通道宽度)。

通常,FPGA 路由是未分段的。也就是说,每个布线段只跨越一个逻辑块,然后在开关盒中终止。通过打开开关盒中的一些可编程开关,可以构建更长的路径。为了获得更高的互连速度,一些 FPGA 架构使用跨越多个逻辑块的更长的路由线。

每当垂直通道和水平通道相交时,就会有一个开关盒。在这种架构中,当一根线进入开关盒时,有三个可编程开关允许它连接到相邻通道段中的另外三根线。这种架构中使用的开关模式或拓扑称为平面或基于域的开关盒拓扑。在这种开关盒拓扑中,轨道编号为 1 的线只连接到相邻通道段中轨道编号为 1 的线,轨道编号为 2 的线只连接到其他轨道编号为 2 的线,依此类推。下图说明了开关盒中的连接。

为了定义 FPGA 的行为,用户提供硬件描述语言 (HDL) 或原理图设计。常见的 HDL 是 VHDL 和 Verilog。然后,使用电子设计自动化工具生成技术映射的网表。然后,网表可以使用称为布局布线的过程(通常由 FPGA 公司的专有布局布线软件执行)拟合到实际的 FPGA 架构。用户将通过时序分析、仿真和其他验证方法验证映射、布局和布线结果。一旦设计和验证过程完成,生成的二进制文件(也使用 FPGA 公司的专有软件)将用于(重新)配置 FPGA。

在典型设计流程中,FPGA 应用开发人员将在设计过程中的多个阶段对设计进行仿真。最初,通过创建测试平台来刺激系统并观察结果,对 VHDL 或 Verilog 中的 RTL 描述进行仿真。然后,在综合引擎将设计映射到网表之后,将网表转换为门级描述,并在此处重复仿真以确认综合过程没有错误。最后,设计在 FPGA 中布局,此时可以添加传播延迟,并使用这些值反向注释到网表上再次运行仿真。

为了降低使用 HDL(与等效的汇编语言相比)进行设计的复杂性,正在采取措施提高设计的抽象级别。Cadence、Synopsys 和 Celoxica 等公司正在推广 SystemC,它将高级语言与并发模型结合在一起,从而为 FPGA 提供比使用传统 HDL 更快的设计周期。基于标准 C 或 C++(带有库或其他扩展以允许并行编程)的方法在 Mentor Graphics 的 Catapult C 工具以及 Impulse Accelerated Technologies 的 Impulse C 工具中找到。Annapolis Micro Systems, Inc. 的 CoreFire 设计套件和 National Instruments LabVIEW FPGA 提供了一种用于高级设计输入的图形数据流方法。SystemVerilog、SystemVHDL 和 Handel-C(来自 Celoxica)等语言试图实现相同的目标,但目标是提高现有硬件工程师的生产力,而不是让 FPGA 更易于现有软件工程师使用。

现代 FPGA 系列扩展了上述功能,包括固定在硅片中的更高级的功能。将这些通用功能嵌入到硅片中可以减少所需的面积,并且与使用基本元件构建它们相比,这些功能可以提高速度。这些示例包括乘法器、通用 DSP 块、嵌入式处理器、高速 IO 逻辑和嵌入式存储器。

为了简化 FPGA 中复杂系统的设计,人们开发了包含预定义复杂功能和电路的库。这些库经过测试和优化,可以加速设计流程。这些预定义电路通常被称为 IP 核,可从 FPGA 供应商和第三方 IP 供应商处获得(通常收费,且通常受专有许可证约束)。其他预定义电路可从开发者社区(例如 OpenCores.org,通常免费,并根据 GPL、BSD 或类似许可证发布)和其他来源获得。

SRAM

针对 FPGA 的嵌入式处理器以软核 IP 的形式提供,用 HDL(如 VHDL 或 Verilog)描述。大多数软核由 FPGA 供应商的专有设计软件提供,并针对其特定的器件。