数字电路/与门

外观

< 数字电路

与门是用于实现逻辑合取的基本门之一。它基本上是一个多输入门,只有一个输出。

它类似于一对串联开关,这些开关操作一个灯泡,该灯泡又与这些开关串联。因此,只有当两个开关都闭合时,灯泡才会亮。从与门的真值表可以看出,只有当所有输入都处于逻辑 1 状态时,输出才会为高电平。

|

|

|

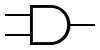

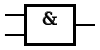

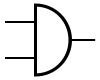

| MIL/ANSI 符号 | IEC 符号 | DIN 符号 |

旁边的逻辑图显示了使用 N 沟道MOSFET构建与门的方法。或者,也可以使用 P 沟道 MOSFET 构建与门。

| A | B | Q | |

|---|---|---|---|

| 0 | 0 | 0 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 |

| 此页面或部分是一个未开发的草稿或大纲。 您可以帮助开发这项工作,或者您可以在项目室中寻求帮助。 |