数字电路/锁存器

锁存器是双稳态多谐振荡器的例子,即具有正好两个稳定状态的器件。这些状态是高输出和低输出。锁存器具有反馈路径,因此信息可以由器件保留。因此,锁存器可以作为存储器件,并且可以在器件通电时存储一位数据。顾名思义,锁存器用于“锁定”信息并保持原位。锁存器与触发器非常相似,但不是同步器件,并且不像触发器那样在时钟边沿上运行。

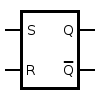

一个SR 锁存器(置位/复位)是一个异步器件:它独立于控制信号工作,仅依赖于 S 和 R 输入的状态。在图像中,我们可以看到一个 SR 锁存器可以通过两个具有交叉反馈回路的 NOR 门来创建。SR 锁存器也可以由 NAND 门组成,但输入被交换和取反。在这种情况下,它有时被称为SR 锁存器。

当向 SR 锁存器的置位线施加高电平输入时,Q 输出变为高电平(而Q 为低电平)。然而,反馈机制意味着Q 输出将保持高电平,即使S 输入再次变为低电平。这就是锁存器如何用作存储器件的方式。相反,复位线上的高电平输入将使Q 输出变为低电平(而Q 为高电平),有效地复位锁存器的“内存”。当两个输入都为低电平时,锁存器“锁存”——它保持在先前设置或复位的状态。

然而,当两个输入同时为高电平时,就会出现问题:它被同时告知要产生高Q 和低Q。这会在电路中产生“竞争状态”——哪个触发器首先成功更改将反馈到另一个触发器并断言自己。理想情况下,两个门是相同的,这是“亚稳态”的,并且器件将处于未定义状态,持续时间不确定。在现实生活中,由于制造方法,一个门总是会获胜,但不可能从装配线上预测它对特定器件将是哪个。因此,S = R = 1 的状态是“非法的”,不应该进入。

| S | R | Q | Q | |

|---|---|---|---|---|

| 0 | 0 | 锁存 | ||

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 亚稳态 | ||

当器件通电时,会发生类似的情况,因为两个输出Q 和Q 都为低电平。同样,由于两个门之间的差异,器件将很快退出亚稳态,但无法预测Q 和Q 中哪个最终会变为高电平。为了避免虚假操作,您应该始终在使用 SR 触发器之前将它们设置为已知初始状态——您不能假设它们将初始化为低电平状态。

在某些情况下,可能需要规定锁存器何时可以和不可以锁存。门控 SR 锁存器是对 SR 锁存器的简单扩展,它提供了一个使能线,该线必须驱动为高电平才能锁存数据。即使现在需要控制线,SR 锁存器也不是同步的,因为如果使能线长时间保持高电平,则输入可以更改输出。(注意:如果时钟提供给控制线,则门控 SR 锁存器被称为SR 触发器,因为输出仅在时钟的边沿触发时才改变。[1])

当使能输入为低电平时,则 AND 门的输出也必须为低电平,因此Q 和Q 输出保持锁存到先前的数据。只有当使能输入为高电平时,锁存器状态才能改变,如真值表所示。当使能线被断言时,门控 SR 锁存器在操作上与 SR 锁存器相同。

使能线有时是时钟信号,但通常是读或写选通。

| 使能 | S | R | Q | Q | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 锁存 | ||

| 0 | 0 | 1 | 锁存 | ||

| 0 | 1 | 0 | 锁存 | ||

| 0 | 1 | 1 | 锁存 | ||

| 1 | 0 | 0 | 锁存 | ||

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 亚稳态 | ||

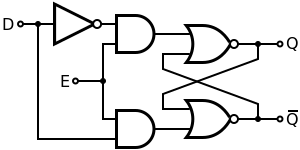

D 锁存器(D 代表“数据”)或透明锁存器是对门控 SR 锁存器的简单扩展,它消除了无效输入状态的可能性。

由于门控 SR 锁存器允许我们在不使用S 或R 输入的情况下锁存输出,我们可以通过使用互补驱动器驱动置位和复位这两个输入来删除其中一个输入:我们删除一个输入并自动使其成为剩余输入的反相。

只要使能线为高电平,D 锁存器就会输出D 输入,否则输出将是使能输入上次为高电平时D 输入的值。这就是它也被称为透明锁存器的原因——当使能被断言时,锁存器被称为“透明”——信号直接通过它传播,就好像它不存在一样。

| 使能 | D | Q | Q | |

|---|---|---|---|---|

| 0 | 0 | 锁存 | ||

| 0 | 1 | 锁存 | ||

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

D 锁存器通常用于集成电路的 I/O 端口,并且可以作为分立器件使用,通常是多封装的。例如,74HC75 是 7400 系列 IC 的一部分,包含四个独立的 D 锁存器。