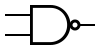

数字电路/与非逻辑

外观

< 数字电路

就像与非门一样,与非门被称为“通用门”,可以组合起来形成任何其他类型的逻辑门。如今,集成电路不再完全由单一类型的门构成。相反,EDA工具被用来将逻辑电路的描述转换为复杂门的网络列表(标准单元)或晶体管(全定制方法)

这是一个与非门:简单来说,只使用一个与非门就可以实现它。

| 目标门 | 与非门构造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

非门是由连接与非门的输入端实现的。由于与非门相当于与门后接非门,因此连接与非门的输入端只留下了非门部分。

| 目标门 | 与非门构造 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||

| ||||||||||

与门是由一个与非门后接一个非门实现的,如下所示。这相当于一个非与非门,即与门。

| 目标门 | 与非门构造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

如果观察与非门的真值表,可以看到如果任何一个输入为0,则输出将为1。然而要成为或门,如果任何一个输入为1,则输出也必须为1。因此,如果输入被反转,则任何高输入都会触发高输出。

| 目标门 | 与非门构造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

与非门只是一个输出被反转的或门。

| 目标门 | 与非门构造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

异或门可以使用四个与非门构建,实现表达式(A与非N)与非(B与非N),其中N=A与非B。这种结构的传播延迟是单个与非门的3倍,并使用四个门。

| 目标门 | 与非门构造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

或者,可以通过考虑析取范式来实现异或门,并注意根据德摩根定律,与非门是输入反转的或门。这种结构使用五个门而不是四个门。

| 目标门 | 与非门构造 |

|---|---|

|

|

异或非门是通过考虑析取范式来实现的,并注意根据德摩根定律,与非门是输入反转的或门。这种结构的传播延迟是单个与非门的3倍,并使用五个门。

| 目标门 | 与非门构造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

或者,可以使用4门版本的异或门与一个反转器。这种结构的传播延迟是单个与非门的4倍(而不是3倍)。

| 目标门 | 与非门构造 |

|---|---|

|

|

- 与非逻辑。与与非门一样,与非门也是通用门。